新風格集成電路設計 創新驅動下的技術變革與產業未來

隨著人工智能、物聯網、5G通信等前沿技術的迅猛發展,傳統集成電路設計模式正面臨前所未有的挑戰與機遇。在這一背景下,以“newstyle”為代表的新風格集成電路設計理念應運而生,它不僅推動了設計方法論的革新,更在技術路徑、產業生態和商業模式上引發了深刻變革。本文將探討新風格集成電路設計的核心內涵、關鍵技術及其對產業未來的影響。

一、新風格集成電路設計的核心內涵

新風格集成電路設計并非單一的技術概念,而是一種融合了敏捷開發、系統級優化、軟硬件協同和開放生態的綜合性設計哲學。其核心在于打破傳統設計流程中的線性思維和孤島效應,強調跨學科整合與快速迭代。

- 敏捷化與模塊化:受軟件工程啟發,新風格設計采用模塊化架構和可復用IP(知識產權核),允許設計團隊并行開發、快速驗證,大幅縮短產品上市周期。例如,基于Chisel或PyMTL等高級硬件描述語言,設計師能以更抽象的層次表達電路功能,提升開發效率。

- 系統級協同優化:傳統設計往往將硬件、軟件和算法割裂,而新風格設計則強調“算法-架構-電路”的一體化優化。尤其在AI芯片領域,通過聯合設計神經網絡模型與硬件加速器,可實現能效比的數量級提升。

- 開放與協作生態:RISC-V開源指令集架構的興起是新風格設計的典型代表。它降低了芯片設計的門檻,促進了全球范圍的協作創新,使中小企業也能參與高端芯片研發。

二、關鍵技術驅動力

新風格集成電路設計的實現,依賴于多項關鍵技術的突破與融合:

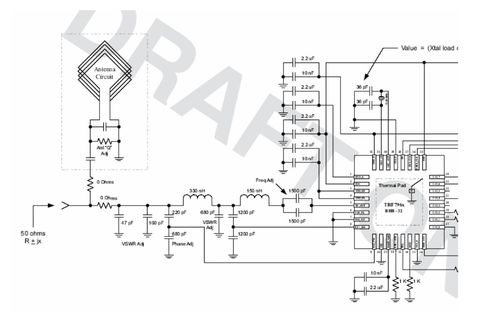

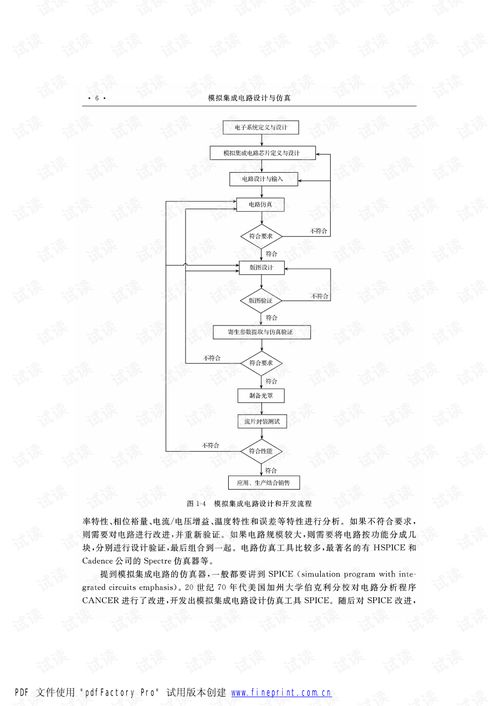

- 高級綜合與電子設計自動化(EDA)工具:新一代EDA工具集成了機器學習算法,能夠自動完成布局布線優化、功耗分析和時序收斂,減輕設計師的重復勞動。例如,谷歌的“Chip Placement with Reinforcement Learning”項目展示了AI在物理設計中的潛力。

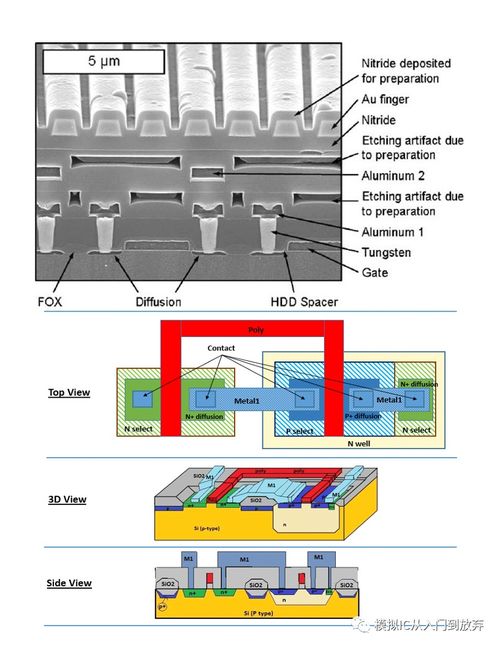

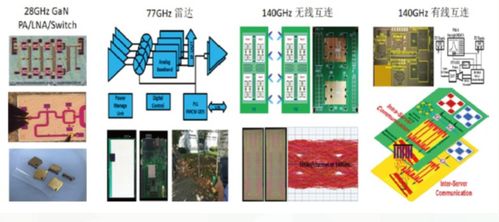

- 異構集成與先進封裝:隨著摩爾定律放緩,通過2.5D/3D封裝技術將不同工藝節點的芯粒(Chiplet)集成,成為提升性能的重要途徑。新風格設計強調以系統級視角規劃芯粒互連與功耗管理,如臺積電的CoWoS和英特爾Foveros技術。

- 設計安全與可信性:在開放生態中,硬件安全成為重中之重。新風格設計將安全機制嵌入架構底層,包括物理不可克隆函數(PUF)、動態加密模塊等,以應對側信道攻擊等威脅。

三、產業影響與未來展望

新風格集成電路設計正在重塑全球半導體產業格局:

- 降低創新門檻:開源工具與IP的普及,使初創公司能夠專注于差異化設計,挑戰傳統巨頭的壟斷。例如,中國在RISC-V生態中涌現出一批創新企業,推動自主可控芯片發展。

- 催生新商業模式:云化EDA平臺(如Cadence Cloud)和設計即服務(DaaS)模式興起,讓設計師能按需使用算力與工具,減少前期投入。芯粒市場促進了IP交易標準化,加速產品迭代。

- 賦能新興應用場景:從自動駕駛到元宇宙,新風格設計的高效性與靈活性正支撐起更復雜的計算需求。隨著量子計算、神經形態計算等前沿方向成熟,集成電路設計將進一步與跨領域技術深度融合。

###

新風格集成電路設計標志著行業從“技術驅動”向“場景驅動”的轉型。它不僅是工具與方法的升級,更是思維模式的革新——從追求單一性能指標,轉向兼顧能效、成本、安全與可擴展性的系統平衡。面對全球供應鏈波動與地緣政治挑戰,擁抱新風格設計將成為各國提升半導體競爭力的關鍵。唯有持續開放協作、深耕底層創新,才能在這場技術浪潮中搶占制高點,構建可持續發展的數字未來。

如若轉載,請注明出處:http://m.deguobao.cn/product/77.html

更新時間:2026-04-08 14:15:28