1833至2004年 世界半導(dǎo)體集成電路發(fā)展史概述

半導(dǎo)體集成電路的發(fā)展是現(xiàn)代科技革命的核心驅(qū)動(dòng)力之一,從1833年半導(dǎo)體效應(yīng)的發(fā)現(xiàn)到2004年集成電路技術(shù)的成熟,這段歷史跨越了近兩個(gè)世紀(jì),見證了人類從基礎(chǔ)科學(xué)探索到工業(yè)化應(yīng)用的偉大歷程。本文將簡(jiǎn)要回顧這一發(fā)展史,重點(diǎn)聚焦于集成電路設(shè)計(jì)的演進(jìn)。

一、早期發(fā)現(xiàn)與理論基礎(chǔ)(1833年-1947年)

半導(dǎo)體集成電路的起源可追溯到1833年,英國(guó)科學(xué)家邁克爾·法拉第首次觀察到硫化銀的半導(dǎo)體特性,即其電阻隨溫度變化而改變。這一發(fā)現(xiàn)為后來(lái)的半導(dǎo)體研究奠定了基礎(chǔ)。直到20世紀(jì)初,量子力學(xué)理論的發(fā)展才為半導(dǎo)體行為提供了科學(xué)解釋。1947年,貝爾實(shí)驗(yàn)室的約翰·巴丁、沃爾特·布拉頓和威廉·肖克利發(fā)明了晶體管,這標(biāo)志著半導(dǎo)體技術(shù)的重大突破,取代了笨重的真空管,為集成電路的誕生鋪平了道路。

二、集成電路的誕生與早期發(fā)展(1958年-1970年代)

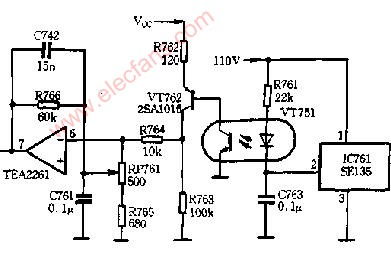

1958年,杰克·基爾比在德州儀器公司成功制造出第一塊集成電路(IC),將多個(gè)晶體管集成在單一硅片上。同年,羅伯特·諾伊斯在仙童半導(dǎo)體公司獨(dú)立開發(fā)出平面工藝,使集成電路的大規(guī)模生產(chǎn)成為可能。這一時(shí)期,集成電路設(shè)計(jì)主要基于簡(jiǎn)單的邏輯門和模擬電路,設(shè)計(jì)方法以手工布局為主,技術(shù)節(jié)點(diǎn)較大(例如微米級(jí)別)。1965年,戈登·摩爾提出“摩爾定律”,預(yù)測(cè)集成電路上晶體管數(shù)量每?jī)赡攴环@成為行業(yè)發(fā)展的指導(dǎo)原則。

三、集成電路設(shè)計(jì)的革新與成熟(1970年代-1990年代)

隨著微處理器(如英特爾4004,1971年)的出現(xiàn),集成電路設(shè)計(jì)進(jìn)入新階段。計(jì)算機(jī)輔助設(shè)計(jì)(CAD)工具的興起,使設(shè)計(jì)過(guò)程自動(dòng)化,提高了復(fù)雜電路的效率。1980年代,超大規(guī)模集成電路(VLSI)技術(shù)普及,設(shè)計(jì)方法從全定制轉(zhuǎn)向半定制和標(biāo)準(zhǔn)單元設(shè)計(jì),降低了成本。設(shè)計(jì)語(yǔ)言如VHDL和Verilog的引入,促進(jìn)了硬件描述語(yǔ)言(HDL)的標(biāo)準(zhǔn)化。1990年代,系統(tǒng)級(jí)芯片(SoC)概念興起,設(shè)計(jì)焦點(diǎn)轉(zhuǎn)向集成處理器、內(nèi)存和外圍功能,推動(dòng)了消費(fèi)電子產(chǎn)品的爆炸式增長(zhǎng)。

四、邁向新世紀(jì):2004年及之前的進(jìn)展

到2004年,集成電路技術(shù)已高度成熟,晶體管尺寸縮小至納米級(jí)別(如90納米工藝),設(shè)計(jì)復(fù)雜度急劇增加。多核處理器和低功耗設(shè)計(jì)成為熱點(diǎn),電子設(shè)計(jì)自動(dòng)化(EDA)工具全面普及,支持從概念到制造的完整流程。知識(shí)產(chǎn)權(quán)(IP)核的復(fù)用和設(shè)計(jì)方法學(xué)的優(yōu)化,進(jìn)一步提升了效率。2004年,半導(dǎo)體行業(yè)已形成全球產(chǎn)業(yè)鏈,集成電路設(shè)計(jì)從單一功能轉(zhuǎn)向多功能、高性能系統(tǒng),為后來(lái)的移動(dòng)互聯(lián)網(wǎng)和物聯(lián)網(wǎng)時(shí)代奠定了基礎(chǔ)。

總結(jié)

從1833年的半導(dǎo)體效應(yīng)發(fā)現(xiàn)到2004年,世界半導(dǎo)體集成電路發(fā)展史是一部創(chuàng)新與應(yīng)用的史詩(shī)。集成電路設(shè)計(jì)從簡(jiǎn)單的手工布局演變?yōu)楦叨茸詣?dòng)化的系統(tǒng)工程,驅(qū)動(dòng)了信息技術(shù)革命。這一歷程不僅體現(xiàn)了科學(xué)探索的持久性,也展示了人類智慧的無(wú)限潛力,為未來(lái)智能社會(huì)奠定了堅(jiān)實(shí)基石。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.deguobao.cn/product/37.html

更新時(shí)間:2026-04-08 15:55:39